中国封装技术卡住英伟达,市场优势逐渐显现

半个多世纪以来,全球集成电路世界经常上演“合久必分,分久必合”的戏码。在产业分工重要分水岭时间节点上经常会出现一些影响因子很高的妙语,比如:

“好汉都有晶圆厂(Real men have fabs)。”

上世纪80年代末,面对风起云涌无晶圆芯片设计公司(Fabless)大潮,AMD创始人杰里·桑德斯(Jerry Sanders)以此语回击Fabless咄咄逼人的态势,一时间舆论大哗。

时至今日,这句话可否再升级一下变成“好汉都有先进封装厂?”

不妨先来看三个有代表性的事实:

更值得注意的是,自去年11月份以来,业界不断传出风声,美国商务部BIS以及两院冷战思维浓重的议员对中国大陆蓬勃发展的先进封装产业“如坐针毡,如芒在背,如鲠在喉”,密谋出台一系列限制措施。

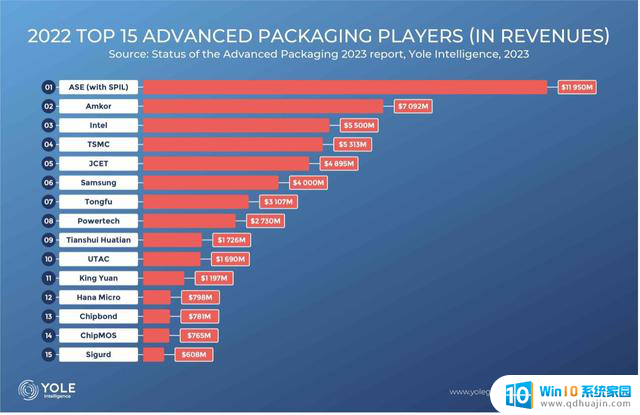

在这一背景下,美国国家标准及技术研究所(NIST)以及战略与国际研究中心(CSIS)先后发布报告并达成共识,认为先进封装已经成为未来十年中美半导体产业的主要厮杀场之一。

封装这样一个曾在几十年内被广泛认为是劳动密集型产业,高附加值挖掘潜力低的环节,如今迎来翻身时刻?

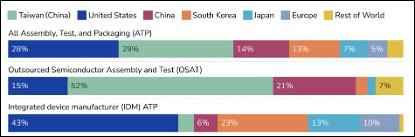

在外包封测环节,中国市场份额高过美国6个百分点(CSIS,2021)

华为海思,全球先进封装的先驱者

先进封装,何为“先进”?显然不同时代对这一词的定义不同,多年前,对于直插式(DIP)和表贴式(QFN)等封装类型来说,焊球阵列(BGA)倒装封装类型无疑属于先进类型。

我们今天谈论的先进封装,是单芯片晶体管架构以及多芯片互联多重因素作用的结果,也是从平面到立体化技术演进的必然。

而促成先进封装得以快速发展的,并非由于制造端二次演进分化下的下游封装测试工厂(OSAT)推动,而是由代工厂来主导,个中缘由并不复杂——只有纯代工厂才能接触到最前沿的芯片设计理念,最能体会在技术层面需要克服的“阿喀琉斯之踵”。

十多年前,台积电团队应该就已经发现,在平面2D封装体系下,随着逻辑芯片和存储芯片之间的数据传输量越来越大,整个芯片传输速度和功耗的利用率越来越低,那么,有没有办法将逻辑芯片和存储芯片贴合得更紧,把引线线宽缩小,从而极大地优化传输速度和功耗?

于是,取代传统封装基板的硅中介层横空出世,Interposer也霎时间成为符合先进封装最标配的内涵指标。

目前在鸿海集团担任半导体策略长的蒋尚义就曾透露,全世界第一个大胆采用台积电硅中介层CoWoS技术的芯片厂,并非目前和台积电一损俱损一荣俱荣的英伟达,而是当时踏入芯片圈不久的华为海思。海思在2014年就对CoWoS做了整体性评估,包括成本和良率等等,决定勇于当先。

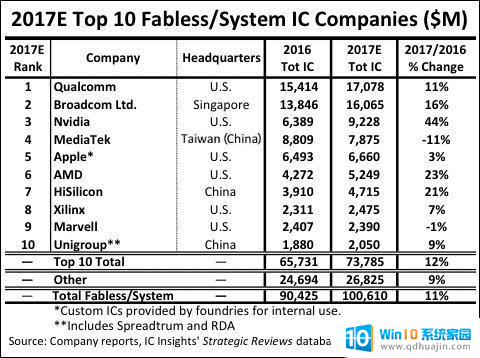

彼时,华为海思经常以一种倔强的身影存在于全球Fabless大潮中。多年后以不断探索勇于创新的莽劲杀进了全球设计公司的前七,外界普遍推论,如果不是美国的强力打压,海思直至今日应该都能将牢牢占据全球设计类公司前三的位置。

在华为海思和台积电的双向奔赴的过程中,也可以体会到为何推动先进封装的主要力量来自纯代工厂而非封测厂,前者毕竟有更大的资金池和容错空间,这对一项新兴技术的上马和落地至关重要。

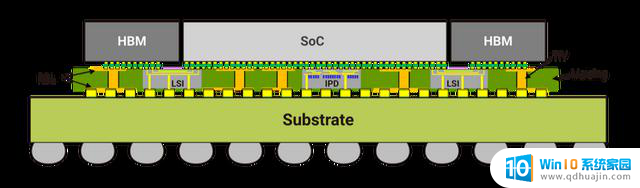

CoWoS(Chip on Wafer on Substrate)是一种2.5D/3D封装技术,可以拆成两部分来看,CoW(Chip on Wafer)指的是晶圆堆叠,WoS(Wafer on Substrate)则是将堆叠的晶圆封装在基板上。而AI GPU上的必需的高带宽内存(HBM)和CoWoS技术是相辅相成的。

HBM的高密度连接和短电路设计要求借助CoWoS这类2.5D封装技术才能实现,这在传统PCB或封装基板上难以完成的。

华为海思敢为天下先,还有一个重要原因是他们是国内最早尝试Chiplet的厂商之一。

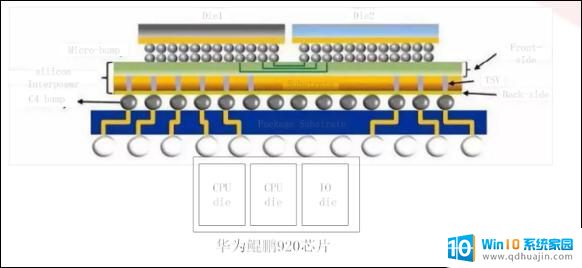

根据台积电公开资料,2014年海思与其合作的64位Arm架构服务器处理器Hi16xx(据查应该为海思第三代服务器处理器16nm鲲鹏916。正式型号Hi1616,正式发布于2015年,2019年初随着920系列的推出,华为将该系列更名为鲲鹏),采用台积电异构CoWoS 3D IC封装工艺,将16nm逻辑芯片与28nm I/O芯片集成在一起,实现了具有成本效益的系统解决方案,这可以视为早期Chiplet实践。

根据华为的另一份公开发表的论文,海思2019年量产的第四代服务器处理器鲲鹏920(7nm制程,正式型号Hi1620) ,通过采用Chiplet技术,将7nm逻辑芯片与16nm I/O芯片等集成在SoC中。

之后,国家知识产权局官网曝光了一份华为海思芯片堆叠技术的发明专利图,利用3D MCM封装的芯片基于Chiplet技术叠加在一起使用,解决性能、面积和成本问题。

这与华为轮值董事长郭平在后来的年度报告发布会上透露的“未来可能会采用多核结构的芯片设计方案,以提升芯片性能”,“用面积换性能,用堆叠换性能”的策略高度一致。尽管华为在先进制程的道路上遇阻,但是Chiplet将继续成为其逆境中的突破口之一。

野火烧不尽,华为海思的先进封装思路后来繁花遍地,其先导性作用还可以从苹果与台积电的合作中体现出来。

当下由台积电首推的使用硅中介层的3D堆叠技术,已经成为ICT行业超热的概念,但在十年前它还只是一个“躁动于母腹中的婴儿”。这个婴儿的助产士则是扇出型封装。苹果iPhone7系列手机的A10应用处理器,同样联手将先进封装彻底带向了一个新的高度。

扇出(Fan-Out)的概念是相对于扇入(Fan-In)而言的,两者都遵循类似的工艺流程。当芯片被加工切割完毕之后,会放置在基于环氧树脂模制化合物的晶圆上,这被称为重构晶圆。然后,在模制化合物上形成再分布层(RDL)。RDL是金属铜连接走线,将封装各个部分进行电气连接。最后,重构晶圆上的单个封装就会被切割。

基于对扇出型封装的理解,我们可以对先进封装的“先进”性有更深层次的认识。比如,标准WLP(fan-in WLP)是在晶圆未进行切片前对芯片进行封装,之后再进行切片分割,完成后的封装大小与芯片的尺寸相同,可以说,立体化、小型化和在保证信号、电源完整性之下的封装密度等等一系列指标,指示着先进封装技术发展的未来。

华为海思的高算力芯片以及苹果的智能手机AP设计理念,都前瞻性地意识到了人工智能和高性能计算等将推动大算力芯片需求的激增。随着摩尔定律趋近极限,晶圆前道工艺的器件和材料都在逼近工艺极限,先进封装这一原本属于“后道”的环节正逐渐成为提升芯片性能的关键。

虽然华为海思自2019年之后不断遭遇各种供应链断供的打压,但其先锋意识带动国内先进封装的上下游产业链做了集体性的铺垫和布局。

“封装技术的重要性恐怕要超过晶圆制造”

近日,中国半导体行业协会理事长陈南翔在接受中央广播电视总台CGTN专访时:“现在是一个应用为王的时代,此外以前大家注重的都是晶圆制造技术,而在当下还需要最新的封装技术的加持。比如当前火热的AI芯片都是需要最先进的晶圆制造技术和最先进的封装技术的。可以预测,在未来非常近的一天,封装技术的重要性恐怕都要超过晶圆制造技术的重要性。”这番表述引发了行业内的广泛热议。

陈南翔所在的长江存储是国内存储行业的龙头企业,以存储器作为小切口观察先进封装,即可一窥这一赛道的巨大成长性。

3D堆叠被主要用于高带宽存储HBM NAND和核心SoC的晶圆堆叠封装技术。美国本土存储半导体龙头美光在2022年推出了232层NAND,同时韩国的三星和海力士等均于2023年实现200+层NAND的量产,存储市场的快速增长将带来3D晶圆级堆叠封装市场的巨大拉升,虽然去年存储市场略有下调,但随着新型存储的量产,预计3D堆叠未来五年的复合年增长率为21.7%。

长期以来,半导体“Value Chain”即价值链的高低划分有一条较为泾渭分明的后道工艺分界线,但目前随着高端AI芯片的火爆,这条Value Chain不得不去接受“Proof of Importance”(重要程度证明)的考验。

这个考验可以通过多重案例得到证明。

首先,有着“人造黄金”之称的英伟达高端AI加速器被先进封装“卡住了脖子”,换言之,英伟达的数据中心GPU/高端AI加速器受制于台积电CoWoS封装的产能的吃紧。

其次,先进封装模糊了前道设备和后道设备的边界,增强了设备的复用性。多种类型的先进封装,如扇出型面板级封装(FOPLP)和CoWoS在应用层面可以试下“复用”。上周业内传出消息,受到CoWoS-L产能不足影响,英伟达将集中力量生产GB200,并以CoWoS-S来生产B200A,而且考虑用FOPLP以解决最新GB200的供应问题。正因为如此,先进封装更多在晶圆层面上进行,基于晶圆制造技术的前道设备和基于晶圆封装的“后道”设备也可以大量复用,于是出现了“中道”这个概念。

CoWoS-L封装架构

再者,先进封装成为异构集成和Chiplet技术得以落地的关键——华为海思在Chiplet技术走向中的敏锐观察力再次得到实践的验证。

随着先进制程下的单颗芯片成本急剧上升,Chiplet日益被视为延续摩尔定律的重要途径。通过将复杂芯片的不同功能分区,采用不同制程工艺生产单独裸片(Die),再使用先进封装互连技术整合在一起,可以突破传统SoC制造面临的诸多挑战(掩膜规模极限和功能极限等),从而提升整体性能,并大幅缩短生产周期,降低设计生产成本。

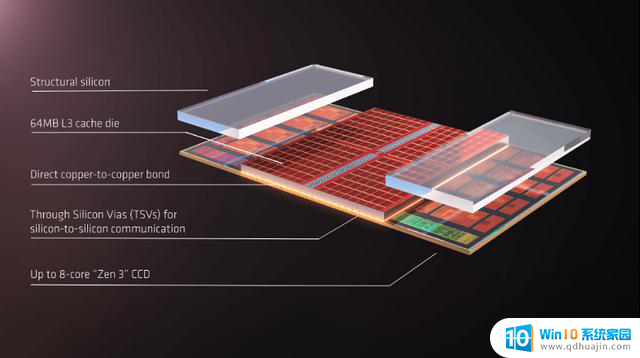

不同类型的异构集成先进封装将为半导体制造创造了新的商业模式,已成为业界的共识,在日渐火热的Chiplet领域,尽管当前仍处于发展初期,但已呈现出异军突起之势。AMD、英特尔、亚马逊AWS等行业领军企业均在其数据中心CPU上采用了Chiplet技术以实现量产,苹果的M1 Ultra设计以及英伟达近日发布的Grace CPU超级芯片也采用了Chiplet理念。

先进封装是Chiplet实现过程中的重要一环,甚至是Chiplet实施的基础和前提。它可以被视为另一种意义上的SiP,并高度融合了晶圆前后道工艺,但是采用Chiplet技术则意味着需要跨多个不同制程的芯片及供应商,每颗裸芯都有不同的架构和物理/逻辑接口,必须考虑如何布局、互连以及提升信号传输质量。

AMD Chiplet理念架构图

必须要指出的是,目前与Chiplet紧密相关的先进封装体系,在互连接口和协议、足够丰富的EDA和IP工具方面还有待完善,但恰恰是不够完美的生态和大量的标准空白,为国内半导体的赶超提供了更多可能性。

国产半导体设备机遇与先进封装

中国半导体行业协会理事长陈南翔并非故作夸张之语,美国人正在不断为这一论断背书。

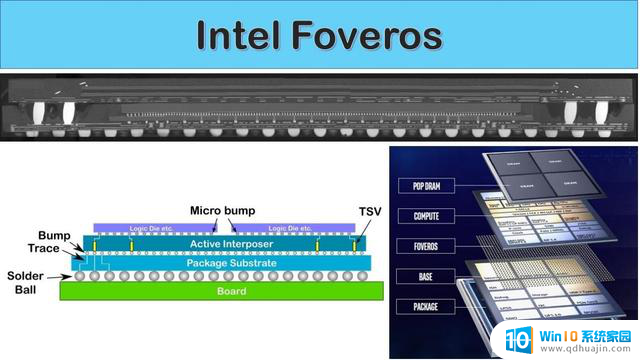

几十年以来,美国半导体代工的“友岸外包”政策让本土化制造端侧产业链急剧萎缩,“制造业回流”计划短时间内难以修补创伤。英特尔最近财务业绩惨不忍睹,但资本市场对其总体成长性同样反应不佳,但华尔街分析师纷纷指出,也许其3D封装技术Foveros是其杀出一条血路的关键。

如前所述,先进封装更多采用前道制造方式来制作后道连接电路,使用设备也大致相同,如2.5D/3D封装TSV技术就需要光刻机、涂胶眼影设备、湿法刻蚀设备等。苏州芯睿科技总经理邱新智先生曾告诉笔者,国内半导体产业虽然在前道制造环节方面相较海外头部企业还有不小的差距,但在先进封装领域的追赶距离更短,可以作为后发赶超的重点突破口,与IC制造的产业大潮相呼应,键合设备在先进封装体系中扮演的角色也越来越重要,先进封装带动的国内键合市场在未来将有狂飙突进式的增长。

此外,贴片机是先进封装过程中最关键、最核心的设备,未来设备需求量与日俱增,近年来出现了华封科技、大连佳峰、无锡翼龙半导体、无锡恩纳基科技等国产化替代进程较快的黑马企业。

划片机被外企高度垄断,国产化替代呼声较大,这也是半导体封装环节中的重要设备,目前国内的晶圆划片机市场主要由日本的DISCO、京东精密等海外企业占据主导地位,但随着国产化替代趋势的逐步明朗,在市场上开始形成了一定的影响力,目前以和研科技、江苏京创先进等企业。已经逐渐实现集团性突破。

引线键合机国产替代空间较大,且国内竞争者较少,国产设备在价格上较海外巨头有优势,预计2023-2025年引线键合机国产替代空间约75亿元,奥特维、德沃、大族封测、凌波微步等企业形成了龙头聚集性优势。

对EDA和IP行业带来换道超车机遇

传统单片集成的SoC因其统一制程之故,芯片上不同的功能模块需要同步进行迭代,导致芯片开发时间长且缺陷数量多。Chiplet技术可以实现功能切分,将制程差异化且部分单元工艺做选择性迭代,可以加速产品的上市周期,减少重新流片和封装的次数,进而降低了芯片企业资金投入成本和研制风险。

换言之,Chiplet可以对芯片上部分单元在工艺上进行最优迭代,针对不同功能选择最合适的工艺制程,在这种范导性技术路线的指引下,延伸出了同构(聚合系统)和异构(分割系统)两种商用实地用例。

早期阶段即芯片分拆和与之对应的先进封装定义协议的“散装化”阶段,统一的标准亟待理清和确定;国内IP龙头企业新耀辉总裁曾克强预计,到2027年左右Chiplet引领的先进封装生态才会真正进入“IP硬化时代”。彼时会诞生一批针对Chiplet技术应运而生的Fabless公司,有源基板供应商、支持集成Chiplet的EDA公司等等,围绕Chiplet先进封装产业的IP生态圈将会更加立体和丰满,相关上下游供应商的协同性也会更加系统化。

结语 我国先进封装已经形成龙头企业集团化作战

目前我国大陆地区的封装厂也在积极布局各类先进封装,扇出型封装,并开发出了具有特色的新工艺,比如长电先进开发的ECP工艺,采用包覆塑封膜替代了液态或者粉体塑封料;华天科技则发出eSiFO技术,由于采用via last TSV方式,可以实现高密度三维互连。

通富微电提出了名为ViSionS的total solution,融合先进封装技术,围绕HPC、存储器、SiP三个方向进行布局。其中2.5D技术已于2021年成功开发,实现样品制作,目前正在配合客户做进一步产品认证和量产规划,预计2022年下半年到2023年,一些客户会逐渐进入2.5D封装量产阶段。2.5D封装的优势在于对硅的依赖度低,在此基础上就可做基础的深度开发工作,与客户产品做高度绑定,因业界普遍判断此将会是一个主流的发展方向。

纵观半个多世纪以来的半导体发展史,各个赛道的玩家有着战略布局重大失误后错失机遇的遗憾,也有不期而遇的良机,唯有勇者能恒立潮头。也许篇头桑德斯的名言并未失效,它只是以另一种面貌在当今重现于世。

本文系观察者网独家稿件,文章内容纯属作者个人观点,不代表平台观点,未经授权,不得转载,否则将追究法律责任。关注观察者网微信guanchacn,每日阅读趣味文章。

中国封装技术卡住英伟达,市场优势逐渐显现相关教程

热门推荐

微软资讯推荐

- 1 如何查看电脑显卡型号及性能信息的方法,轻松掌握显卡信息

- 2 如何打开NVIDIA显卡控制面板的详细步骤解析,一步步教你轻松设置显卡参数

- 3 微软推荐迁移至Win11新版Outlook,邮件和日历应用今年终止支持

- 4 Windows可以直接运行安卓手机App了,轻松在电脑上使用安卓应用

- 5 国产游戏显卡 唯一DX12!摩尔线程要上市了,性能超越国外同类产品

- 6 三季度手机处理器市场数据:苹果收入最高,联发科总量第一

- 7 微软Win10 22H2/21H2推送11月累积更新:修复打印机问题最新

- 8 索泰显卡的性能与性价比全面评测:索泰显卡性价比如何?

- 9 数亿台电脑面临“退休”危机!Windows 10用户抓紧升级!

- 10 微软确认Win10/Win11锁屏未来支持编辑、移除MSN小部件

win10系统推荐

- 1 萝卜家园ghost win10 64位家庭版镜像下载v2023.04

- 2 技术员联盟ghost win10 32位旗舰安装版下载v2023.04

- 3 深度技术ghost win10 64位官方免激活版下载v2023.04

- 4 番茄花园ghost win10 32位稳定安全版本下载v2023.04

- 5 戴尔笔记本ghost win10 64位原版精简版下载v2023.04

- 6 深度极速ghost win10 64位永久激活正式版下载v2023.04

- 7 惠普笔记本ghost win10 64位稳定家庭版下载v2023.04

- 8 电脑公司ghost win10 32位稳定原版下载v2023.04

- 9 番茄花园ghost win10 64位官方正式版下载v2023.04

- 10 风林火山ghost win10 64位免费专业版下载v2023.04

系统教程推荐

- 1 给电脑软件换图标 电脑软件图标修改方法

- 2 台式电脑前侧耳机没声音 Win11电脑插耳机为什么没有声音

- 3 怎么把桌面文件夹存到d盘 Win10系统如何将桌面文件保存到D盘

- 4 win11桌面图片如何设置 如何在Windows11上设置个性化壁纸

- 5 win11开机自启动便筏 win11开机自启动软件设置方法

- 6 怎样把搜狗输入法放到任务栏 怎么把搜狗输入法固定到任务栏

- 7 键盘锁死无法打字 键盘怎么办锁住了

- 8 电脑上不显示耳机选项 win10电脑插上耳机没有声音

- 9 笔记本电脑刚开机就自动关机是怎么回事 笔记本电脑开机后几秒钟自动关机

- 10 台式电脑里面有蓝牙吗 电脑有没有蓝牙怎么查看